лучший способ кодирования D триггера

недавно я видел некоторый D-триггер RTL-код в verilog, как это:

module d_ff(

input d,

input clk,

input reset,

input we,

output q

);

always @(posedge clk) begin

if (~reset) begin

q <= 1'b0;

end

else if (we) begin

q <= d;

end

else begin

q <= q;

end

end

endmodule

слова q <= q; надо?

2 ответов

необходимо ли утверждение q

нет, это не так, и в случае ASIC это может фактически увеличить площадь и энергопотребление. Я не уверен, как современные FPGAs справляются с этим. Во время синтеза инструмент увидит это утверждение и потребует, чтобы q обновлялся на каждом положительном крае часов. Без этого последнего предложения else инструмент может только обновлять q всякий раз, когда выполняются данные условия.

на ASIC это означает синтез инструмент может вставлять ворота часов(при условии, что библиотека имеет один) вместо mux. Для одного DFF это может быть хуже, так как ворота часов обычно намного больше, чем mux, но если q 32 бита, тогда экономия может быть очень значительной. Современные инструменты могут автоматически определить, соответствует ли число DFFs с помощью общего включения определенному порогу, а затем выбрать часовой затвор или mux соответствующим образом.

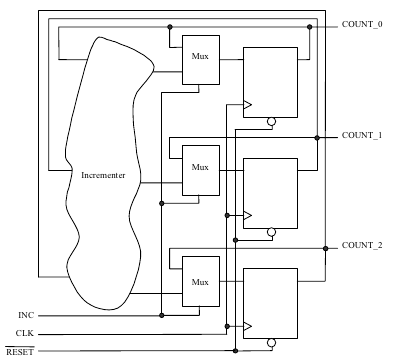

в этом случае инструмент нуждается в 3 muxes plus extra маршрутизация

always @(posedge CLK or negedge RESET)

if(~RESET)

COUNT <= 0;

else if(INC)

COUNT <= COUNT + 1;

else

COUNT <= COUNT;

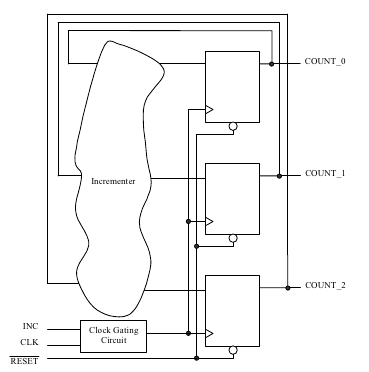

здесь инструмент использует один часовой затвор для всех DFFs

always @(posedge CLK or negedge RESET)

if(~RESET)

COUNT <= 0;

else if(INC)

COUNT <= COUNT + 1;

Что касается моделирования, удаление этого оператора не должно ничего менять, так как q должен иметь тип reg (или логику в SystemVerilog) и должен содержать его значение.

кроме того, большинство инструментов синтеза должны генерировать одну и ту же схему в обоих случаях, так как q обновляется с использованием неблокирующего назначения. Возможно, лучшим кодом было бы использовать always_ff вместо always (если ваш инструмент поддерживает его). Таким образом, компилятор будет проверять, что q всегда обновляется с помощью генерируется неблокирующее назначение и последовательная логика.