Определяется ли переполнение integer в VHDL?

мне было интересно, определено ли переполнение integer в VHDL. Я не смог найти ничего в спецификации 2002 года.

в качестве примера (обратите внимание, что это может не компилироваться, это просто общий пример...):

entity foo is port (

clk : std_logic

);

end entity;

architecture rtl of foo is

signal x : integer range 0 to 2 := 0;

begin

process (clk)

begin

if rising_edge(clk) then

x <= x + 1;

end if;

end process;

end architecture;

понятно, что x будет идти от 0 до 1, а потом 2. Определено ли, что произойдет при следующем приращении? Это неопределенное поведение?

3 ответов

для стенда испытания для rtl foo в ghdl:

ghdl-r foo_tb --wave=foo_tb.ghw

./foo_tb:ошибка: проверки отказ в foo_tb.vhdl: 15

./foo_tb: ошибка: ошибка моделирования

я добавил предложение контекста к сущности и архитектуре Foo Билла:

library ieee;

use ieee.std_logic_1164.all;

entity foo is port (

строка 15-это присвоение сигнала x:

x <= x + 1;

это ошибка моделирования (происходит во время выполнения).

из IEEE 1076-1993:

7.2.4 добавление операторов

добавление операторов + и - предопределены для любого числового типа и имеют обычный математический смысл.

это означает, что результат оператора " + " может находиться вне ограничения подтипа x. Обратите внимание, что функция, объявленная для обеспечения перегрузки для"+", не позволяет указать подтип результата. (Возвращаемое значение может быть объектом, объявленным с указанием подтипа, который можно определить диапазон значений или длину массива).

и 12.6.2 распространение значений сигнала

для обновления сигнала в течение заданного цикла моделирования процесс ядра сначала определяет управляющие и эффективные значения этого сигнала. Затем процесс ядра обновляет переменную, содержащую текущее значение сигнала, новым эффективным значением, следующим образом:

a) если S-сигнал некоторого типа, который не тип массива, действующее значение S используется для обновления текущего значения S. выполняется проверка, что действующее значение S принадлежит подтипу S. при сбое этой проверки подтипа возникает ошибка. Наконец, эффективное значение S присваивается переменной, представляющей текущее значение сигнала.

если результат добавления не соответствует ограничению подтипа целевого x, он создаст ошибку. Это ограничение подтипа предоставлено объявлением object x, которое предоставляет указание подтипа для целого числа (диапазона).

Ошибка времени выполнения приводит к завершению моделирования для реализации, совместимой с LRM.

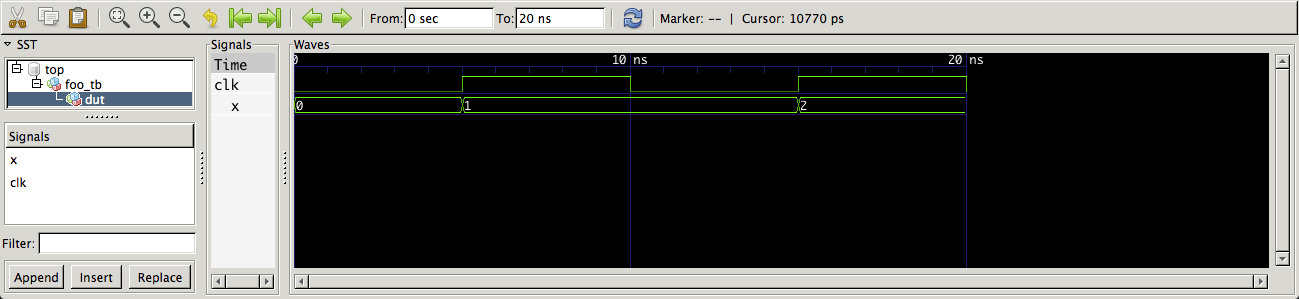

без стандартизированного формата для сообщения об ошибках ghdl не обеспечивает текущее время моделирования. Это можно найти, изучая произведенную форму волны:

форма волны довольно обновляется после 20 НС. Следующий запланированное событие:

library ieee;

use ieee.std_logic_1164.all;

entity foo_tb is

end entity;

architecture foo of foo_tb is

signal clk: std_logic := '0';

begin

DUT:

entity work.foo

port map (

clk => clk

);

CLOCK:

process

begin

wait for 5 ns;

clk <= not clk;

if now > 30 ns then

wait;

end if;

end process;

end architecture;

был бы восходящий край clk на 25 НС.

таким образом, это говорит нам, как ограниченное целое число создает ошибку переполнения.

как насчет целого числа без ограничения подтипа:

architecture fum of foo is

signal x : integer := INTEGER'HIGH - 2;

begin

process (clk)

begin

if rising_edge(clk) then

x <= x + 1;

end if;

end process;

end architecture;

мы определяем x как неограниченное целое число, это значение по умолчанию, где мы ожидаем переполнения x.

пакет standard explicity объявляет целое число"+":

-- function "+" (anonymous, anonymous: INTEGER) return INTEGER;

ожидаемый результат снаружи диапазон целого числа, если, как мы видим, " + " имеет обычное математическое значение.

однако из зависимого от реализации объявления в стандарте пакета:

type integer is range -2147483648 to 2147483647;

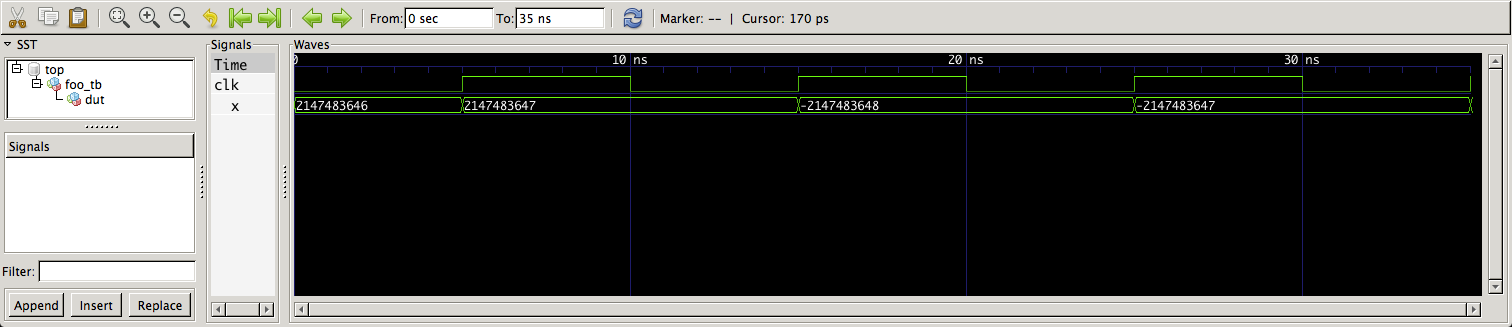

и моделирования:

мы видим значение x обернуть вокруг.

назначение результата оператора " + " не нарушило никаких ограничений:

3 типа:

набор возможных значений для объекта данный тип может быть подвергнут условию, которое называется ограничением (случай, когда ограничение не налагает никаких ограничений, также включен); значение считается удовлетворяющим ограничению, если оно удовлетворяет соответствующему условию. Подтип-это тип вместе с ограничением. Значение считается принадлежащим подтипу данного типа, если оно принадлежит типу и удовлетворяет ограничению; данный тип называется базовым типом подтипа. Тип - это подтип самого себя; такой подтип называется быть неограниченным (это соответствует условию, которое не налагает никаких ограничений). Базовый тип типа-это сам тип.

в нашей второй архитектуре и нет ограничений, но нет возможных значений вне объявленного диапазона для типа INTEGER. Вместо этого значение переворачивается.

семантика для VHDL была построена, чтобы не требовать обнаружения здесь, и это соответствует математическим операциям на одномерных массивах элементов представление двоичных битов (аппаратных средств).

любой приличный симулятор остановится там с сообщением об ошибке, указывающим именно на дополнение, которое переполнено. (Xilinx Isim-это только приличный симулятор, если вы не забыли включить проверки, в последний раз, когда я смотрел)

жуткий, если вы сделали слишком много программирования C годами!

синтез будет делать все, что экономит оборудование, (в этом случае без выходов, оптимизировать X и процесс полностью!) поэтому лучше всего поймать такого рода ошибку в симуляции.

Integer overflow (и underflow)-это поведение, определяемое реализацией в VHDL. Я не могу процитировать спецификацию на данный момент, но если вы внимательно прочтете, вы увидите, что почти все о целочисленных диапазонах определяется реализацией за пределами минимального поддерживаемого диапазона (-2**31 до 2**31).

большинство реализаций VHDL на 32-разрядных машинах на самом деле вести себя так, как если бы они были 32-разрядными целыми числами завершения 2 (например, как целые числа машины ведут себя на этих платформах) и 64-разрядными реализации, как правило, имеют 64-разрядные целые числа, но вы не можете рассчитывать на это.

для вашего конкретного примера, если вы используете целочисленный подтип с диапазоном, если вы пытаетесь назначить значение вне этого диапазона, это ошибка и создаст утверждение во время выполнения. (Синтезаторы, с другой стороны, будут делать все странные вещи, которые они хотят-обычно они переполняются, как если бы это было целое число дополнения 2).