Почему rising edge предпочтительнее falling edge

Шлепанцы (Регистрам ...) обычно срабатывают при подъеме или падении края. Но в основном в коде вы видите if-предложение, которое использует запуск восходящего края. На самом деле я никогда не видел код с спаду.

Почему это? Это потому, что, естественно, программисты используют rising edge, потому что они привыкли, или это из-за какого-то физического/аналогового закона/факта, где Программирование rising edge быстрее/проще/энергоэффективнее/... ?

4 ответов

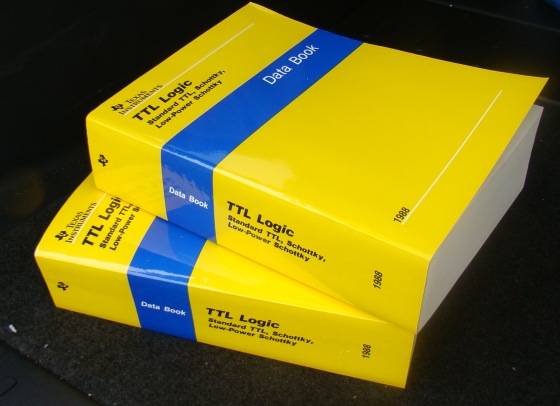

Как говорит зеннехой, это условность-но один возвращается к тому, когда логика была сделана в дискретные чипы с несколькими воротами или стоит в них. Эти пакеты flipflops всегда были запущены ... насколько я помню,но, может быть, кто-то с лучшим воспоминанием о желтых книгах поправит меня!

поэтому, когда синтез пришел, без сомнения, все чувствовали себя комфортно, продолжая таким образом!

не более чем вопрос условности.

использование восходящего края более распространено, и большинство библиотек компонентов используют восходящий край. Это означает, что для использования этих библиотек необходимо также использовать восходящие ребра, или добавить логику синхронизации часов, или сохранить пути настолько короткими, что задержка составляет менее половины такта. Просто использование восходящих краев везде, безусловно, проще всего.

когда вы конструируете (одиночн-край) DFF в обломоке, вы должны выбрать на котором (поднимая или падая) край часов он будет работать. Это решение не зависит от подхода реализации (т. е. master-slave или pulsed-latch), и оно не изменяет количество транзисторов в самом DFF.

поскольку положительный край является типичным значением по умолчанию (как в FPGAs), для работы с отрицательным краем часов обычная процедура состоит в том, чтобы просто использовать положительный край DFF с перевернутой версией тактовый сигнал подключен к его тактовому порту. Если это сделано локально (рядом с портом часов DFF), то действительно необходимы два дополнительных транзистора (для создания CMOS-инвертора для часов).

Это несколько вопрос конвенции, но если вы посмотрите на дизайн падения против подъема края, есть только разница добавленного инвертора, и оказалось, что на 2 транзистора меньше на подъеме края

но есть проекты, которые используют оба, например, в некоторых кэшах данных, которые вы пишете на rising edge и читаете на falling edge, или наоборот, в зависимости от выбора дизайна!

хороший вопрос, и попробуйте или возьмите курс (возможно, онлайн) на цифровом интегральные схемы