В чем разница между reg и wire в модуле verilog

в чем разница между reg и проводом? Когда мы должны использовать reg и когда мы должны использовать провод в модуле verilog. Я также иногда замечал, что вывод объявляется снова как reg. Е. Г Рег q В Д флип-флоп. Я где - то читал это: "целевой вывод процедурных операторов присваивания должен иметь тип данных reg."Что такое процедурные заявления о назначении? Я тщательно прогуглил это, но не смог найти четкого объяснения.

3 ответов

провод:-

> Wires are used for connecting different elements. They can be treated

> as physical wires. They can be read or assigned. No values get stored

> in them. They need to be driven by either continuous assign statement

> or from a port of a module.

Reg: -

> Contrary to their name, regs don't necessarily correspond to

> physical registers. They represent data storage elements in

> Verilog/SystemVerilog. They retain their value till next value is

> assigned to them (not through assign statement). They can be

> synthesized to FF, latch or combinatorial circuit. (They might not be

> synthesizable !!!)

провода и правила присутствуют с таймфрейма Verilog. SystemVerilog добавлено новый тип данных под названием логика. И следующий вопрос-Что такое этот логический тип данных и чем он отличается от нашего старого доброго wire / reg.

логика:-

как мы видели, тип данных reg-бит вводят в заблуждение в языке Verilog. Логика SystemVerilog-это тип данных, для того, чтобы удалить выше путаница. Идея заключается в том, что новый тип данных называется logic, который по крайней мере, не создается впечатление, что это аппаратное синтезируемое. Тип данных Logic не позволяет использовать несколько драйверов. Это последнее назначение выигрывает поведение в случае нескольких назначений (что подразумевает он не имеет аппаратной эквивалентности). Типы данных Reg/Wire дают X, если несколько водители пытаются управлять ими с помощью разных ценности. Логический тип данных просто присваивает последнее значение назначения. Следующая разница между reg / wire и логика заключается в том, что логика может управляться как назначением блока, так и выходом порт и внутри процедурного блока, как это

logic a; assign a = b ^ c; // wire style always (c or d) a = c + d; // reg style MyModule module(.out(a), .in(xyz)); // wire style

процедурные блоки относятся к always, always_ff, always_comb, always_latch, initial etc. блоки. В то время как процедурные операторы присваивания относятся к присвоению значений reg, integer и т. д., а не провода(сетки).

wire элементы должны быть непрерывно движется на что-то, и не может хранить значение. Отныне им присваиваются значения с помощью непрерывное задание заявления.

reg можно использовать для создания регистры в процедурных блоков. Таким образом, он может магазине какое-то значение.

reg элементов can использоваться в качестве вывода внутри фактический модуль декларация. Но,reg элементов не может быть подключен к выходному разъему модуля экземпляров.

таким образом, a reg может управлять провод as RHS на assign заявление. С другой стороны, a провод может управлять reg в as RHS процедурного блока.

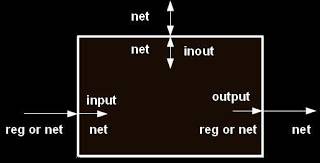

для ясного представления об объявлении reg или wire, см. изображение ниже:

Итак, всякий раз, когда вывод последовательной логики, которая хранит / содержит некоторое значение, объявляет эту переменную / порт как reg. Вот,Q это reg внутри модуль, но в то время как создание экземпляра этот модуль внутри другого модуля, затем этот порт должен быть подключен к wire.

помните, что wire может только выводить комбинационную логику, в то время как reg может выводить либо комбинационную, либо последовательную логику.

блог Дэйва является хорошим источником подробной информации. Для получения дополнительной информации см. синтезирующий разница и Verilog wire-reg ссылки.

простая разница между reg и проводом, reg используется в комбинационной или последовательной цепи в verilog и провод используется в комбинационной цепи

reg используется для хранения значения, но провод непрерывно управляется какой-то вещью, и провод подключен к порту, когда инициализация модуля, но reg не подключен